- 312 pages

- English

- ePUB (mobile friendly)

- Available on iOS & Android

eBook - ePub

AVR RISC Microcontroller Handbook

About this book

The AVR RISC Microcontroller Handbook is a comprehensive guide to designing with Atmel's new controller family, which is designed to offer high speed and low power consumption at a lower cost. The main text is divided into three sections: hardware, which covers all internal peripherals; software, which covers programming and the instruction set; and tools, which explains using Atmel's Assembler and Simulator (available on the Web) as well as IAR's C compiler.

- Practical guide for advanced hobbyists or design professionals

- Development tools and code available on the Web

Trusted by 375,005 students

Access to over 1 million titles for a fair monthly price.

Study more efficiently using our study tools.

Information

1

Some Basics

In the following chapters we will use some special terms that are perhaps not so familiar to a beginner. Some explanations should make the world of microcontroller terms and functionality more transparent.

1.1 Architecture

All microcontrollers have more or less the same function groups. Internally we find memory for instructions and data and a central processing unit (CPU) for handling the program flow, manipulating the data, and controlling the peripherals.

Figure 1-1 shows the basic function blocks in a microcontroller. The CPU communicates with each of these function blocks (memory and peripherals).

Figure 1-1 Microcontroller function blocks.

To build a powerful microcontroller, it is important to reduce the tasks carried out from the CPU itself and to optimize the handling of the remaining tasks.

On the left side of Figure 1-1, peripherals are arranged. These peripherals react with the world outside, or in more technical terms, with the process. In modern microcontrollers, the peripherals relieve the CPU by handling the external events separately.

In an asynchronous serial communication, for example, the CPU transmits the character to be sent only to the serial port. The required serialization and synchronization are performed by the serial port itself. On the other side, receiving a character is important for the CPU only when all bits are stored in a buffer and are ready for an access of the CPU.

A port is built by a certain number of connections between the microcontroller and the process, often a factor of 8. It usually supports a bitwise digital input and/or output (I/O).

Serial ports communicate with other external components by means of serial communication protocols. Asynchronous and synchronous serial communications must be differentiated. Both kinds of serial communication have their own building blocks—Universal Asynchronous Receiver and Transmitter (UART) for asynchronous communication, and Serial Peripheral Interface (SPI) for synchronous communication. In Figure 1-1 this differentiation is not shown.

Because the microcontroller is designed for process-related applications with real-time character, some other function groups are implemented in a microcontroller.

Modern microcontrollers have a fairly comfortable interrupt system. An interrupt breaks the running program to process a special routine, called the interrupt service routine. Some external events require an immediate reaction. These events generate an interrupt; the whole system will be frozen, and in an interrupt service routine the concerning event is handled before the program goes on. If the microcontroller has to process many interrupts, an interrupt controller can be helpful.

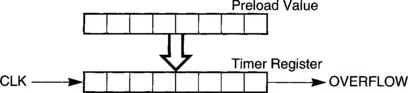

To fulfill timing conditions, microcontrollers have one or more timers implemented. The function blocks usually work as timer and/or counter subsystems. In the simplest case, we have an 8-bit timer register. Its contents will be incremented (or decremented) with each clock cycle (CLK). Any time the value 255 (or 0) is reached, the register will overflow (or underflow) with the next clock. This overflow (or underflow) is signalized to the CPU. The actual delay depends on the preload value.

If the preload value equals zero, then the overflow will occur after 256 clock periods. If the preload value equals 250, in an up-counter the overflow will occur after six clock cycles. A block diagram of a simple timer is shown in Figure 1-2.

Figure 1-2 Timer.

Last but not least, we had in Figure 1-1 an AD/DA subsystem. For adaptions to a real-world process, analog-to-digital and/or digital-to-analog converters are often required. This is not the place to discuss all features of these more or less complex subsystems. Some microcontrollers include such an AD/DA subsystem or can control an external one. In other cases, only analog comparators are integrated.

Thus, each peripheral has its own intelligence for handling external events and to realize preprocessing.

On the right side of Figure 1-1, we find the microprocessor part (CPU and memory). The memory contains program and data. CPU and memory are connected through a bus system. This architecture—called “von Neumann” architecture—has some drawbacks.

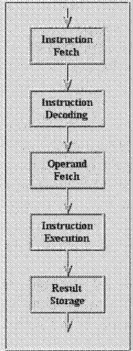

In Figure 1-3 instruction handling is explained. Before an instruction can be operated, it must first be fetched from memory. Next, the program counter must be incremented. After this incrementation, the program counter points to the next instruction in memory. Before execution of the fetched instruction, it has to be decoded. As a result of this decoding, further memory accesses for operands or addresses are possible. The instruction execution includes arithmetic or logical operations, followed by storage of the result back to the memory.

Figure 1-3 Instruction handling.

It seems not so difficult to understand that the handling of one instruction requires more than one memory access. Usually, one instruction manipulates one data byte. Therefore, several memory accesses are inconsistent with the manipulation of one data byte by one instruction.

Very large scale integration (VLSI) technology has made it possible to build very fast CPUs. However, slow memory access times inhibits this evolution. This fundamental problem of the von Neumann architecture is called the “von Neumann bottleneck.”

To avoid these limitations, system designers implement some sort of cache memory—a fast memory buffer between the main memory and the CPU. Another, and most recent approach, is to separate the paths to the memory system for instructions and data—the “Harvard” architecture.

The RISC design philosophy also tries to eliminate the “von Neumann bottleneck” by strict limitation of memory operations by means of many internal registers.

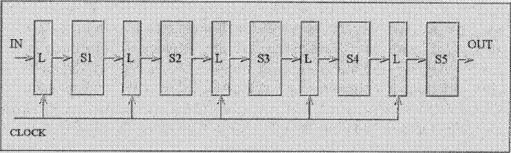

In order to increase performance, pipelining is widely used in modern microprocessor architectures. A basic linear pipeline consists of a cascade of processing stages.

The instruction unit in a microprocessor architecture can consist of pipeline stages for instruction fetch, instruction decode, operand fetch, execute instruction, and store results. Using such a technique for preparing an execute operation allows a new instruction to be executed every clock cycle. In this design, five different instructions are flowing simultaneously in the pipeline. Figure 1-4 shows an instruction pipeline for all steps of the instruction handling according to Figure 1-3.

Figure 1-4 Instruction pipeline.

All blocks in the pipeline are pure combinational circuits performing arithmetic or logic operations over the data stream flowing through the pipeline. T...

Table of contents

- Cover image

- Title page

- Table of Contents

- Copyright

- Preface

- Chapter 1: Some Basics

- Chapter 2: Hardware Resources of AVR Microcontrollers

- Chapter 3: Handling the Hardware Resources

- Chapter 4: Development Tools

- Chapter 5: Example Programs

- Appendix A: Part Numbering System

- Appendix B: Pin Configurations

- Appendix C: Schematics of SIMMSTICK Modules

- Appendix D: Register and Bit Definitions

- Appendix E: Some Fundamentals of RS-232

- Appendix F: Some Fundamentals of RS-422 and RS-485

- Appendix G: 8-Bit Intel Hex File Format

- Appendix H: Decimal-to-Hex-to-ASCII Converter

- Appendix I: Overview of Atmel’s Application Notes and Software

- Appendix J: Literature

- Appendix K: Contacts

- Index

Frequently asked questions

Yes, you can cancel anytime from the Subscription tab in your account settings on the Perlego website. Your subscription will stay active until the end of your current billing period. Learn how to cancel your subscription

No, books cannot be downloaded as external files, such as PDFs, for use outside of Perlego. However, you can download books within the Perlego app for offline reading on mobile or tablet. Learn how to download books offline

Perlego offers two plans: Essential and Complete

- Essential is ideal for learners and professionals who enjoy exploring a wide range of subjects. Access the Essential Library with 800,000+ trusted titles and best-sellers across business, personal growth, and the humanities. Includes unlimited reading time and Standard Read Aloud voice.

- Complete: Perfect for advanced learners and researchers needing full, unrestricted access. Unlock 1.4M+ books across hundreds of subjects, including academic and specialized titles. The Complete Plan also includes advanced features like Premium Read Aloud and Research Assistant.

We are an online textbook subscription service, where you can get access to an entire online library for less than the price of a single book per month. With over 1 million books across 990+ topics, we’ve got you covered! Learn about our mission

Look out for the read-aloud symbol on your next book to see if you can listen to it. The read-aloud tool reads text aloud for you, highlighting the text as it is being read. You can pause it, speed it up and slow it down. Learn more about Read Aloud

Yes! You can use the Perlego app on both iOS and Android devices to read anytime, anywhere — even offline. Perfect for commutes or when you’re on the go.

Please note we cannot support devices running on iOS 13 and Android 7 or earlier. Learn more about using the app

Please note we cannot support devices running on iOS 13 and Android 7 or earlier. Learn more about using the app

Yes, you can access AVR RISC Microcontroller Handbook by Claus Kuhnel in PDF and/or ePUB format, as well as other popular books in Computer Science & Computer Engineering. We have over one million books available in our catalogue for you to explore.