- English

- ePUB (mobile friendly)

- Available on iOS & Android

eBook - ePub

About this book

Since its commercialization in 1971, the microprocessor, a modern and integrated form of the central processing unit, has continuously broken records in terms of its integrated functions, computing power, low costs and energy saving status. Today, it is present in almost all electronic devices. Sound knowledge of its internal mechanisms and programming is essential for electronics and computer engineers to understand and master computer operations and advanced programming concepts. This book in five volumes focuses more particularly on the first two generations of microprocessors, those that handle 4- and 8- bit integers. Microprocessor 4 – the fourth of five volumes – addresses the software aspects of this component. Coding of an instruction, addressing modes and the main features of the Instruction Set Architecture (ISA) of a generic component are presented. Futhermore, two approaches are discussed for altering the flow of execution using mechanisms of subprogram and interrupt. A comprehensive approach is used, with examples drawn from current and past technologies that illustrate theoretical concepts, making them accessible.

Trusted by 375,005 students

Access to over 1 million titles for a fair monthly price.

Study more efficiently using our study tools.

Information

1

Coding and Addressing Modes

This chapter focuses on two important characteristics of Instruction Set Architecture (ISA) (cf. § V1-3.5), which are instruction encoding and addressing modes.

1.1. Encoding and formatting an instruction

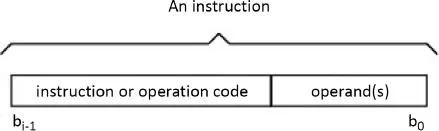

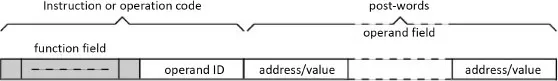

The instruction1 is represented in a computer using a binary word in the format i bits, a multiple of the format n of the data and, in general, a multiple of the byte. We use the expression machine code to mean all those binary words representing the instruction to be executed. Instruction encoding depends on the architecture of the target processor. It is formed at least of an instruction code and, potentially, of one or more operands as Figure 1.1 illustrates.

Figure 1.1. Breakdown of an instruction

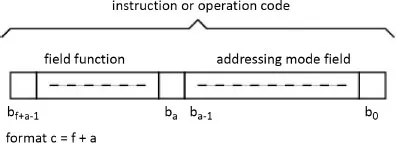

This instruction can be broken down into fields2. The instruction code, also called operation code (abridged to opcode), in format c, has one or more fields. The essential one is the function code. It defines the operation to be executed. Its format of f bits defines the maximum number of instructions F (= 2f) in the instruction set3. Other fields can be added to this such as, for example, one that specifies the addressing mode (the addressing mode field) of the operands to the format as Figure 1.2 illustrates (VAX4 approach from the Digital Equipment Corporation (DEC)). The processor therefore has 2a addressing modes. Besides simplifying the encoding, one benefit is to separate the encoding of the function from that of the address, which makes it possible to make the instruction set symmetrical (cf. § 3.1.3). This instruction code generally takes the format of the data n of the processor to optimize access to primary memory. Since in our example n is fixed, the architect of the microprocessor or MPU (MicroProcessor Unit) must therefore compromise between the number of instructions and the number of addressing modes if the field exists. One field may be favored to the detriment of the other.

Figure 1.2. An example of the structure of an operation code

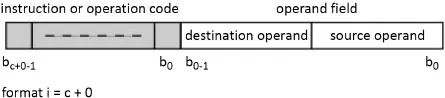

If the instruction requires, the operation code is followed by one or more operand fields (Figure 1.3), and their number is dependent on the operation (unary or binary) and the architecture. This operand field in the format o bits makes it possible to specify, depending on the addressing mode chosen, the value of the reference of the location of the operand needed for calculation or, potentially, the result. An operand's storage location, which is imposed by the programmer, compiler or linker or architecture, is a register or memory location. An instruction to one operand is called a “monadic”, and one with two operands, “dyadic”. When there are two operands, we speak of source and destination operands or sink operands or sometimes simply left and right operands. We cite the VAX mini-computer with a variable format as an example of encoding. The operation code included one to two bytes. It was eventually followed by no more than six operand specifiers, mainly address specifiers, making it possible to design the operand. The MPU MC6800 instruction format included one to three bytes, the first being an operation code indicating the addressing mode.

Figure 1.3. Format of an instruction with two operands

Table 1.1 shows the different address combinations for IA-32 instruction set (IA for Intel Architecture, also called i386). Combinations not indicated are not possible either due to the architecture or to their incoherence. We cite impossible memory (to) memory combinations in most architectures, as it is necessary to pass through a register and an immediate-register or immediate-memory, which cannot be done because of the impossibility of allocating a value to a constant.

Table 1.1. Possible address combinations in family IA-32

| Operands | |

| Destination | Source |

| Register | Immediate |

| Memory | Immediate |

| Register | Register |

| Memory | Register |

| Register | Memory |

The identification field (ID) of the operand(s) specifies the format and addressing mode (register or memory reference) as well as the direction of transfer (Figure 1.4). In a RISC microprocessor (Reduced Instruction Set Computer, this will be covered in a future book by the author on microprocessors), this field is included in the instruction's code through simplification and in view of the reduced number of instructions and addressing modes.

Figure 1.4. An instruction with several operands

By construction, the format of the instruction is fixed (fixed length), short or long, or variable (variable length). The value of a fixed format is a multiple of the byte in general. Its value will have a direct consequence for the incrementation value of the Program Counter (PC, cf. § V3-3.1.3). The benefit is that it will be possible to align the instructions (cf. § 3.1.2), thus accelerating memory reading or writing by reducing the number of memory accesses. The division of the instruction into subfields, for example, one for the instruction class (cf. Chapter 2), the second for the function, the third for the type of operands and the last for the operands and a unique format allowing simplification of the hardware, the counterpart being a larger format. A variable fo...

Table of contents

- Cover

- Table of Contents

- Title page

- Copyright

- Quotation

- Preface

- Introduction

- 1 Coding and Addressing Modes

- 2 Instruction Set and Class

- 3 Additional Concepts

- 4 Subroutine

- 5 Interrupt Mechanism

- Conclusion of Volume 4

- Exercises

- Appendix

- Acronyms

- References

- Index

- End User License Agreement

Frequently asked questions

Yes, you can cancel anytime from the Subscription tab in your account settings on the Perlego website. Your subscription will stay active until the end of your current billing period. Learn how to cancel your subscription

No, books cannot be downloaded as external files, such as PDFs, for use outside of Perlego. However, you can download books within the Perlego app for offline reading on mobile or tablet. Learn how to download books offline

Perlego offers two plans: Essential and Complete

- Essential is ideal for learners and professionals who enjoy exploring a wide range of subjects. Access the Essential Library with 800,000+ trusted titles and best-sellers across business, personal growth, and the humanities. Includes unlimited reading time and Standard Read Aloud voice.

- Complete: Perfect for advanced learners and researchers needing full, unrestricted access. Unlock 1.4M+ books across hundreds of subjects, including academic and specialized titles. The Complete Plan also includes advanced features like Premium Read Aloud and Research Assistant.

We are an online textbook subscription service, where you can get access to an entire online library for less than the price of a single book per month. With over 1 million books across 990+ topics, we’ve got you covered! Learn about our mission

Look out for the read-aloud symbol on your next book to see if you can listen to it. The read-aloud tool reads text aloud for you, highlighting the text as it is being read. You can pause it, speed it up and slow it down. Learn more about Read Aloud

Yes! You can use the Perlego app on both iOS and Android devices to read anytime, anywhere — even offline. Perfect for commutes or when you’re on the go.

Please note we cannot support devices running on iOS 13 and Android 7 or earlier. Learn more about using the app

Please note we cannot support devices running on iOS 13 and Android 7 or earlier. Learn more about using the app

Yes, you can access Microprocessor 4 by Philippe Darche in PDF and/or ePUB format, as well as other popular books in Computer Science & Computer Engineering. We have over one million books available in our catalogue for you to explore.