Encyclopedia Of Thermal Packaging, Set 2: Thermal Packaging Tools (A 4-volume Set)

Set 2: Thermal Packaging Tools(A 4–Volume Set)

- 1,396 pages

- English

- ePUB (mobile friendly)

- Available on iOS & Android

Encyclopedia Of Thermal Packaging, Set 2: Thermal Packaging Tools (A 4-volume Set)

Set 2: Thermal Packaging Tools(A 4–Volume Set)

About this book

Please click here for information on Set 1: Thermal Packaging Techniques

Thermal and mechanical packaging — the enabling technologies for the physical implementation of electronic systems — are responsible for much of the progress in miniaturization, reliability, and functional density achieved by electronic, microelectronic, and nanoelectronic products during the past 50 years. The inherent inefficiency of electronic devices and their sensitivity to heat have placed thermal packaging on the critical path of nearly every product development effort in traditional, as well as emerging, electronic product categories.

Successful thermal packaging is the key differentiator in electronic products, as diverse as supercomputers and cell phones, and continues to be of pivotal importance in the refinement of traditional products and in the development of products for new applications. The Encyclopedia of Thermal Packaging, compiled in four multi-volume sets ( Set 1: Thermal Packaging Techniques, Set 2: Thermal Packaging Tools, Set 3: Thermal Packaging Applications, and Set 4: Thermal Packaging Configurations ) will provide a comprehensive, one-stop treatment of the techniques, tools, applications, and configurations of electronic thermal packaging. Each of the author-written sets presents the accumulated wisdom and shared perspectives of a few luminaries in the thermal management of electronics.

Set 2: Thermal Packaging Tools

The second set in the encyclopedia, Thermal Packaging Tools, includes volumes dedicated to thermal design of data centers, techniques and models for the design and optimization of heat sinks, the development and use of reduced-order “compact” thermal models of electronic components, a database of critical material thermal properties, and a comprehensive exploration of thermally-informed electronic design. The numerical and analytical techniques described in these volumes are among the primary tools used by thermal packaging practitioners and researchers to accelerate product and system development and achieve “correct by design” thermal packaging solutions.

The four sets in the Encyclopedia of Thermal Packaging will provide the novice and student with a complete reference for a quick ascent on the thermal packaging “learning curve,” the practitioner with a validated set of techniques and tools to face every challenge, and researchers with a clear definition of the state-of-the-art and emerging needs to guide their future efforts. This encyclopedia will, thus, be of great interest to packaging engineers, electronic product development engineers, and product managers, as well as to researchers in thermal management of electronic and photonic components and systems, and most beneficial to undergraduate and graduate students studying mechanical, electrical, and electronic engineering.

Foreword

Foreword (English) (42 KB)

Foreword (Japanese) (342 KB)

Please click here for information on Set 1: Thermal Packaging Techniques

Thermal and mechanical packaging — the enabling technologies for the physical implementation of electronic systems — are responsible for much of the progress in miniaturization, reliability, and functional density achieved by electronic, microelectronic, and nanoelectronic products during the past 50 years. The inherent inefficiency of electronic devices and their sensitivity to heat have placed thermal packaging on the critical path of nearly every product development effort in traditional, as well as emerging, electronic product categories.

Successful thermal packaging is the key differentiator in electronic products, as diverse as supercomputers and cell phones, and continues to be of pivotal importance in the refinement of traditional products and in the development of products for new applications. The Encyclopedia of Thermal Packaging, compiled in four multi-volume sets ( Set 1: Thermal Packaging Techniques, Set 2: Thermal Packaging Tools, Set 3: Thermal Packaging Applications, and Set 4: Thermal Packaging Configurations ) will provide a comprehensive, one-stop treatment of the techniques, tools, applications, and configurations of electronic thermal packaging. Each of the author-written sets presents the accumulated wisdom and shared perspectives of a few luminaries in the thermal management of electronics.

Set 2: Thermal Packaging Tools

The second set in the encyclopedia, Thermal Packaging Tools, includes volumes dedicated to thermal design of data centers, techniques and models for the design and optimization of heat sinks, the development and use of reduced-order “compact” thermal models of electronic components, a database of critical material thermal properties, and a comprehensive exploration of thermally-informed electronic design. The numerical and analytical techniques described in these volumes are among the primary tools used by thermal packaging practitioners and researchers to accelerate product and system development and achieve “correct by design” thermal packaging solutions.

The four sets in the Encyclopedia of Thermal Packaging will provide the novice and student with a complete reference for a quick ascent on the thermal packaging “learning curve,” the practitioner with a validated set of techniques and tools to face every challenge, and researchers with a clear definition of the state-of-the-art and emerging needs to guide their future efforts. This encyclopedia will, thus, be of great interest to packaging engineers, electronic product development engineers, and product managers, as well as to researchers in thermal management of electronic and photonic components and systems, and most beneficial to undergraduate and graduate students studying mechanical, electrical, and electronic engineering.

Foreword

Foreword (English) (42 KB)

Foreword (Japanese) (342 KB)

Readership: Packaging engineers, electronic product development engineers, and product managers, as well as researchers in thermal management of electronic and photonic components and systems, and most beneficial to undergraduate and graduate students studying mechanical, electrical, and electronic engineering. Key Features:

Frequently asked questions

- Essential is ideal for learners and professionals who enjoy exploring a wide range of subjects. Access the Essential Library with 800,000+ trusted titles and best-sellers across business, personal growth, and the humanities. Includes unlimited reading time and Standard Read Aloud voice.

- Complete: Perfect for advanced learners and researchers needing full, unrestricted access. Unlock 1.4M+ books across hundreds of subjects, including academic and specialized titles. The Complete Plan also includes advanced features like Premium Read Aloud and Research Assistant.

Please note we cannot support devices running on iOS 13 and Android 7 or earlier. Learn more about using the app.

Information

Table of contents

- Cover

- Half Title

- Title Page

- Copyright

- Foreword to the Encyclopedia of Thermal Packaging

- Dedication

- Contents

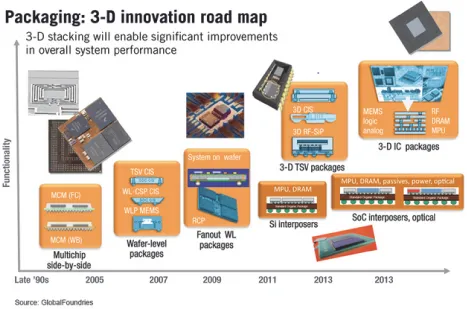

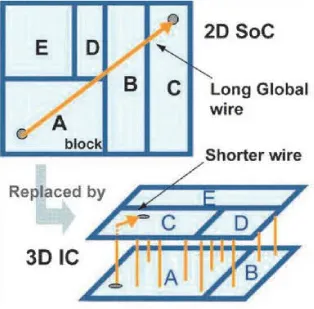

- Chapter 1. A Review of Cooling Road Maps for 3D Chip Packages

- Chapter 2. Thermal Performance Mapping of Direct Liquid Cooled 3D Chip Stacks

- Chapter 3. Dynamic Thermal Management Considering Accurate Temperature-Leakage Interdependency

- Chapter 4. Energy Reduction and Performance Maximization Through Improved Cooling

- Chapter 5. Optimal Choice of Heat Sinks from an Industrial Point of View

- Chapter 6. Synthetic Jets for Heat Transfer Augmentation in Microelectronics Systems

- Chapter 7. Recent Advance in Thermoelectric Devices for Electronics Cooling

- Chapter 8. Energy Efficient Solid-State Cooling for Hot Spot Removal

- Chapter 9. An Overview of the Use of Phase Change Materials for the Thermal Management of Transient Portable Electronics: Benefits and Challenges

- Chapter 10. Estimation of Cooling Performance of Phase Change Material (Pcm) Module

- Chapter 11. Optimization Under Uncertainty for Electronics Cooling Design

- Chapter 12. Hydrophilic Cnt-Sintered Copper Composite Wick for Enhanced Cooling

- Chapter 13. A Cabinet Level Thermal Test Vehicle to Evaluate Hybrid Double-Sided Cooling Schemes

- Chapter 14. Energy Efficiency and Reliability Risk Mitigation of Data Centers Through Prognostics and Health Management

- Chapter 15. Damage Pre-Cursors Based Assessment of Accrued Thermo-mechanical Damage and Remaining Useful Life in Field Deployed Electronics

- Chapter 16. Towards Embedded Cooling - Gen 3 Thermal Packaging Technology

- Author Index

- Subject Index

- Cover

- Half Title

- Title Page

- Copyright

- Foreword to the Encyclopedia of Thermal Packaging

- Preface

- Contents

- Acknowledgements

- Chapter 1. Data Centers and Thermal Management Approaches

- Chapter 2. Thermal Modeling of Data Centers

- Chapter 3. Dynamic Thermal Modeling of Data Centers

- Chapter 4. Containment

- Chapter 5. Multi-scale Modeling of Electronics Cabinets

- Chapter 6. Thermal Measurements and Their Use in Data Centers

- Author Index

- Subject Index

- Cover

- Half Title

- Title Page

- Copyright

- Dedication

- Foreword to the Encyclopedia of Thermal Packaging

- Preface

- Contents

- Acknowledgements

- Chapter 1. Fundamentals of Electronic Component Thermal Resistance

- Chapter 2. Historical Overview of Proposals for Enhanced Thermal Metrics

- Chapter 3. Star-Shaped Compact Models Including 2R Models

- Chapter 4. Boundary-Condition-Independent Compact Models

- Chapter 5. Theoretical Framework of Compact Thermal Models — Steady Problems

- Chapter 6. Techniques to Create Compact Thermal Models — Steady State Problems

- Chapter 7. Techniques to Create Compact Thermal Models — Dynamic Problems

- Chapter 8. Experimental Calibration of Compact Thermal Models

- Chapter 9. Compact Thermal Models in Practice

- Chapter 10. Standardization Aspects of IC and LED Compact Models

- Chapter 11. Concluding Remarks

- Appendix. A Nomenclature of Thermal Resistance

- Appendix B. Glossary of Frequently Used Terms and Acronyms

- Appendix C. Testing and Characterization Standards for Chip Packages

- Appendix D. Green’s Function for Conduction Equation

- Appendix E. Eliminating Temperature Dependence of Thermal Conductivity

- Author Index

- Subject Index

- Cover

- Half Title

- Title Page

- Copyright

- Foreword to the Encyclopedia of Thermal Packaging

- Preface

- Contents

- Chapter 1. Thermal Challenges

- Chapter 2. Thermally-Aware Design

- Chapter 3. Runtime Thermal Management Techniques

- Chapter 4. Ongoing Efforts

- Author Index

- Subject Index

- About the Authors

- About the Editor-in-Chief