1.1.1 The Cortex®-M3 and Cortex-M4 processors

The Cortex®-M3 and Cortex-M4 are processors designed by ARM®. The Cortex-M3 processor was the first of the Cortex generation of processors, released by ARM in 2005 (silicon products released in 2006). The Cortex-M4 processor was released in 2010 (released products also in 2010).

The Cortex-M3 and Cortex-M4 processors use a 32-bit architecture. Internal registers in the register bank, the data path, and the bus interfaces are all 32 bits wide. The Instruction Set Architecture (ISA) in the Cortex-M processors is called the Thumb® ISA and is based on Thumb-2 Technology which supports a mixture of 16-bit and 32-bit instructions.

The Cortex-M3 and Cortex-M4 processors have:

• Three-stage pipeline design

• Harvard bus architecture with unified memory space: instructions and data use the same address space

• 32-bit addressing, supporting 4GB of memory space

• On-chip bus interfaces based on ARM AMBA® (Advanced Microcontroller Bus Architecture) Technology, which allow pipelined bus operations for higher throughput

• An interrupt controller called NVIC (Nested Vectored Interrupt Controller) supporting up to 240 interrupt requests and from 8 to 256 interrupt priority levels (dependent on the actual device implementation)

• Support for various features for OS (Operating System) implementation such as a system tick timer, shadowed stack pointer

• Sleep mode support and various low power features

• Support for an optional MPU (Memory Protection Unit) to provide memory protection features like programmable memory, or access permission control

• Support for bit-data accesses in two specific memory regions using a feature called Bit Band

• The option of being used in single processor or multi-processor designs

The ISA used in Cortex-M3 and Cortex-M4 processors provides a wide range of instructions:

• General data processing, including hardware divide instructions

• Memory access instructions supporting 8-bit, 16-bit, 32-bit, and 64-bit data, as well as instructions for transferring multiple 32-bit data

• Instructions for bit field processing

• Multiply Accumulate (MAC) and saturate instructions

• Instructions for branches, conditional branches and function calls

• Instructions for system control, OS support, etc.

In addition, the Cortex-M4 processor also supports:

• Single Instruction Multiple Data (SIMD) operations

• Additional fast MAC and multiply instructions

• Saturating arithmetic instructions

• Optional floating point instructions (single precision)1

Both the Cortex-M3 and Cortex-M4 processors are widely used in modern microcontroller products, as well as other specialized silicon designs such as System on Chips (SoC) and Application Specific Standard Products (ASSP).

In general, the ARM Cortex-M processors are regarded as RISC (Reduced Instruction Set Computing) processors. Some might argue that certain characteristics of the Cortex-M3 and Cortex-M4 processors, such as the rich instruction set and mixed instruction sizes, are closer to CISC (Complex Instruction Set Computing) processors. But as processor technologies advance, the instruction sets of most RISC processors are also getting more complex, so much so that this traditional boundary between RISC and CISC processor definition can no longer be applied.

There are a lot of similarities between the Cortex-M3 and Cortex-M4 processors. Most of the instructions are available on both processors, and the processors have the same programmer’s model for NVIC, MPU, etc. However, there are some differences in their internal designs, which allow the Cortex-M4 processor to deliver higher performance in DSP applications, and to support floating point operations. As a result, some of the instructions available on both processors can be executed in fewer clock cycles on the Cortex-M4.

1.1.2 The Cortex®-M processor family

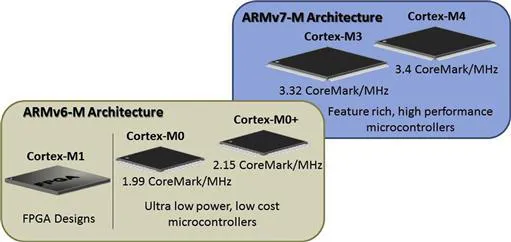

The Cortex®-M3 and Cortex-M4 processors are two of the products in the ARM® Cortex-M processor family. The whole Cortex-M processor family is shown in Figure 1.1.

FIGURE 1.1 The Cortex-M processor family

The Cortex-M3 and Cortex-M4 processors are based on ARMv7-M architecture. Both are high-performance processors that are designed for microcontrollers. Because the Cortex-M4 processor has SIMD, fast MAC, and saturate arithmetic instructions, it can also carry out some of the digital signal processing applications that traditionally have been carried out by a separate Digital Signal Processor (DSP).

The Cortex-M0, Cortex-M0+, and the Cortex-M1 processors are based on ARMv6-M, which has a smaller instruction set. Both Cortex-M0 and Cortex-M0+ are very small size in terms of gate count, with just about 12K gates2 in minimum configuration, and are ideal for low-cost microcontroller products. The Cortex-M0+ processor has the most state-of-the-art low power optimizations, and has more available optional features.

The Cortex-M1 processor is designed specifically for FPGA applications. It has Tightly Coupled Memory (TCM) features that can be implemented using memories inside the FPGA, and the design allows high clock frequency operations in advanced FPGA. For example, it can run at over 200 MHz in Altera Stratix III FPGA.

For general data processing and I/O control tasks, the Cortex-M0 and Cortex-M0+ processors have excellent energy efficiency due to the low gate count design. But for applications with complex data processi...